初识 SPI 通信协议 |

您所在的位置:网站首页 › verilog spi协议 › 初识 SPI 通信协议 |

初识 SPI 通信协议

|

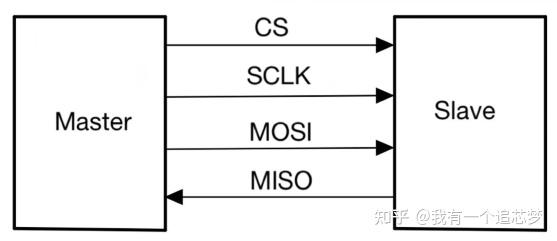

每当听师兄说起 SPI 协议 ,总是以简单两字一笔带过,今天趁着“老板”不在,偷偷研究了一番...... SPI (Serial Peripheral Interface)协议,是一种串行外设接口协议。四线制 SPI (现在只讨论四线制,言外之意就是还有三线制)是一种全双工、高速的同步通信总线,一般只有四根线构成通信传输通路,这样大大节省了主从设备之间的管脚资源、布局布线,同时由于 SPI 协议操作简单,因此在越来越多的芯片中备受欢迎(也就是支持 SPI 通信协议)。 一、SPI 通信协议原理介绍1. SPI 结构 SPI 通信协议中比较常用的是主从工作方式,一个主设备可以连接一个以上的从设备,通过 从设备的片选信号(CS)选择从设备。SPI 四线是指:CS、SCLK、MOSI、MISO。  四线 SPI 主从设备连接图 四线 SPI 主从设备连接图注:Master主设备,Slave从设备 CS :Slave设备使能信号,一般都是由Master发出,习惯上我们称其为片选信号; SCLK :Slave的时钟信号,由Master设备产生; MOSI :Master设备数据输出,Slave设备数据输入,也就是Master设备要输出一 组channel 控制信息去告诉Slave接下来需要做什么(一般channel信息包含Slave设备的工作模式、地址通道等信息); MISO :Master设备数据输入,Slave设备数据输出,也就是Slave设备要输出与上一组Master设备输入的channel 信息相对应的数据,这个数据就是我们实际想要的数据。 2. SPI 工作模式 SPI通信协议有四种不同的模式 ,由时钟极性CPOL来配置SCLK在空闲时,应该处于的状态(高/低);由时钟相位CPHA来配置在第几个边沿进行采样。 MODE0:CPOL=0,CPHA=0:此时空闲态时,SCLK处于低电平,数据采样是在第1个边沿,也就是SCLK由低电平到高电平的跳变,所以数据采样是在上升沿,数据发送是在下降沿。 MODE1:CPOL=0,CPHA=1:此时空闲态时,SCLK处于低电平,数据发送是在第1个边沿,也就是SCLK由低电平到高电平的跳变,所以数据采样是在下降沿,数据发送是在上升沿。 MODE2:CPOL=1,CPHA=0:此时空闲态时,SCLK处于高电平,数据采集是在第1个边沿,也就是SCLK由高电平到低电平的跳变,所以数据采集是在下降沿,数据发送是在上升沿。 MODE3:CPOL=1,CPHA=1:此时空闲态时,SCLK处于高电平,数据发送是在第1个边沿,也就是SCLK由高电平到低电平的跳变,所以数据采集是在上升沿,数据发送是在下降沿。 二、Verilog实现SPI 通信协议驱动编写SPI协议实现与AD模块的数据通信以 AD7888 芯片为例,附芯片使用手册链接: 使用一个芯片,首先需要了解这个芯片的工作机制(工作原理),在官网找对应的官方使用手册(User Guide)是最保险也是最合适的。对于AD7888芯片,通过查询手册找到需要的信息如下:  AD7888 引脚功能图 AD7888 引脚功能图很容易得到想要的结果: a. AD7888模块有8个模拟输入端(AIN1~AIN8); b. 带有CS'、SCLK、DIN、DOUT; c. 可选择不同的参考电压。  AD7888 手册截图 AD7888 手册截图AD7888芯片精度为12bit,支持8通道ADC,支持SPI/QSPI等协议接口,同时由手册可知最大速率可达 2.5 Mhz(具体看手册内容) 。  AD7888 控制通道数据格式 AD7888 控制通道数据格式通过PM1,PM0可配置AD7888的工作模式,常用的模式是{PM1=0,PM0=0}的  AD7888 Normal-Mode Operation AD7888 Normal-Mode Operation使用 SPI 协议与AD7888通信的时序,在第0个时钟的上升沿/下降沿使能AD7888的片选信号CS',然后进行数据传输(共16个周期),同时在数据传输完时在时钟下降沿将CS翻转。 Verilog代码实现 FPGA通过SPI协议与AD7888进行通信 `timescale 1ns/1ns //AD7888 module spi_drive_test( input i_sclk, input i_rst_n, input i_spi_din, output o_spi_cs, output o_spi_dout, input i_wr_en,//write pluse output o_wr_done, input [7:0] i_wr_channel, input i_rd_en,//read pluse output o_rd_done, output [11:0] o_rd_data ); reg s_cs_n; reg s_wr_en; reg [4:0] s_cnt; reg [16:0] s_channel; reg [15:0] s_data_buffer; reg s_rd_en_d1; reg s_rd_en_d2; always @(posedge i_sclk or negedge i_rst_n)begin if(!i_rst_n) s_wr_en |

【本文地址】

今日新闻 |

推荐新闻 |